Product Summary

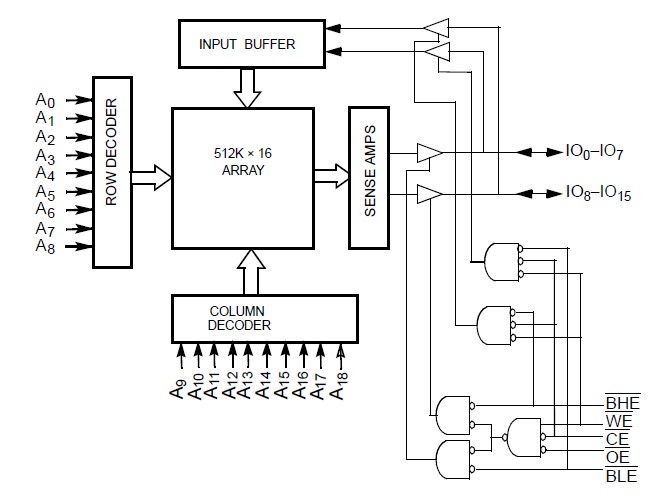

The CY7C1051DV33-10ZSXI is a high-performance CMOS Static RAM organized as 512K words by 16 bits. Write to the CY7C1051DV33-10ZSXI by taking Chip Enable (CE) and Write Enable (WE) inputs LOW. If Byte LOW Enable (BLE) is LOW, then data from IO pins (IO0–IO7), is written into the location specified on the address pins (A0–A18). The CY7C1051DV33-10ZSXI is available in a 44-pin TSOP II package with center power and ground (revolutionary) pinout, as well as a 48-ball fine-pitch ball grid array (FBGA) package.

Parametrics

CY7C1051DV33-10ZSXI absolute maximum ratings: (1)Storage Temperature: –65℃ to +150℃; (2)Ambient Temperature with Power Applied: –55℃ to +125℃; (3)Supply Voltage on VCC to Relative GND: –0.5V to +4.6V; (4)DC Voltage Applied to Outputs in High-Z State: –0.3V to VCC + 0.3V; (5)DC Input Voltage: –0.3V to VCC + 0.3V; (6)Current into Outputs (LOW): 20 mA; (7)Static Discharge Voltage: >2001V(per MIL-STD-883, Method 3015); (8)Latch-up Current: >200 mA.

Features

CY7C1051DV33-10ZSXI features: (1)High speed tAA = 10 ns; (2)Low active power ICC = 110 mA @ 10 ns; (3)Low CMOS standby power ISB2 = 20 mA; (4)2.0V data retention; (5)Automatic power-down when deselected; (6)TTL-compatible inputs and outputs; (7)Easy memory expansion with CE and OE features; (8)Available in lead-free 48-ball FBGA and 44-pin TSOP II packages.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

CY7C1051DV33-10ZSXI |

Cypress Semiconductor |

SRAM 8M FAST ASYNC IND HI SPD SRAM |

Data Sheet |

|

|

||||||||||||

|

CY7C1051DV33-10ZSXIT |

Cypress Semiconductor |

SRAM 8M FAST ASYNC HI SPD SRAM |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))